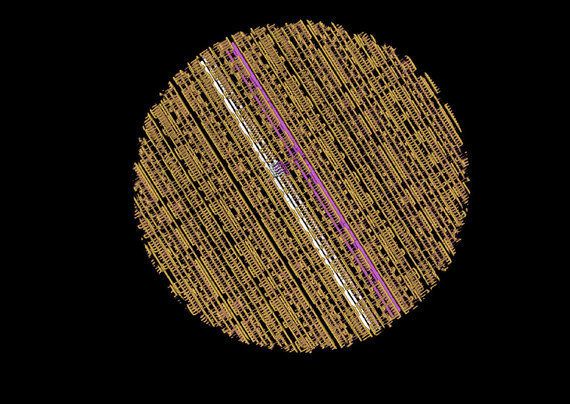

インテルのプロセッサチップの内部構造を捉えた3D画像。試料の直径は10 μmで、配線の幅は最も細いもので約45 nm。Credit: Mirko Holler

コンピューターチップにはナノメートルスケールのデバイスや回路がますます詰め込まれるようになっているため、最も小さなフィーチャーを解像してチップの設計や検査を可能にできる新しい顕微鏡技術が必要になる。

Advertisement

X線画像化法は、非破壊的な高分解能画像化に比類なく適しており、今回M Hollerたちは、最近開発されたコンピューター画像化法であるX線タイコグラフィーを使って、集積回路の高分解能三次元画像を生成している。

彼らは、既知のフィーチャーを有する回路でX線タイコグラフィーを検証し、次に、22 nm技術で製造したインテルのプロセッサチップにこれを適用して、このデバイスの詳細な三次元マップを最小14.6 nmの分解能で得ている。

この技術は、チップ製造時の品質管理に役立つ可能性がある。

Nature 543, 7645

2017年3月16日

原著論文:

doi:10.1038/nature21698

【関連記事】

スマート薄膜カラーディスプレイ Nature511, 7508 2014年7月10日

自己組織化するマイクロロボットを目指して Nature503, 7474 2013年11月7日

細胞用のナノ温度計 Nature500, 7460 2013年8月1日

ラマン分光による単一分子の内部構造解明 Nature498, 7452 2013年6月6日